#### Description

ITR-511 is a high performance CMOS linear image sensor with 2048 pixels. The ITR-511 can be used as a socket-compatible replacement for the Sony ILX511B CCD linear sensor. Advanced CMOS technology is used to emulate the signal level scheme of the ILX511B ensuring both signal level and pin compatibility. In comparison with sensors based on CCD technology, the ITR-511 offers better or equal performance. The ITR-511 requires a single 5V power supply.

#### Features

- CMOS image sensor to replace former CCD

- 2048 active pixels aligned as in the former CCD

- 14µm x 196µm pixels for optical compatibility

- Single 5 volt supply no higher voltages needed

- Emulates signals used with the former CCD

- Output signal compatible with existing readout circuits

- Supports clock rates in excess of 2 MHz

- Available with temporary window for UV applications

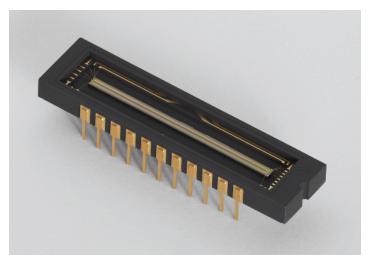

- Ceramic package and gold-plated pins

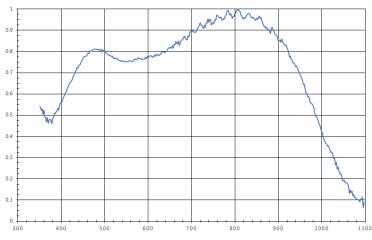

- High red and near-infrared response with low ripple

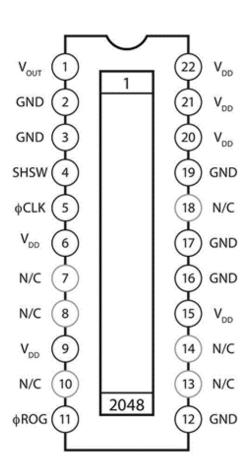

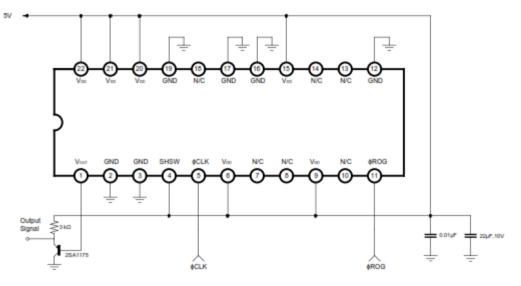

#### **Pinout Configuration**

The pinout on the ITR-511 is identical to that of the ILX511B except that pins used for high-voltage supplies are not connected. This permits use of existing power circuits.

ITR-511-SW

#### **Relative Quantum Efficiency**

#### Pinout

The pin layout for the ITR-511 is the same as in the ILX511B except that the ITR-511 requires only a single 5 volt supply. The pin for VGG is left unconnected for socket compatibility.

| #  | ILX511B | ITR-511 | Signal Description             |

|----|---------|---------|--------------------------------|

| 1  | VOUT    | VOUT    | Signal output                  |

| 2  | GND     | GND     | Ground                         |

| 3  | GND     | GND     | Ground                         |

| 4  | SHSW    | SHSW    | S/H switch, ON:gnd, OFF:vdd    |

| 5  | ΦCLK    | ΦCLK    | Falling edge Clock             |

| 6  | VDD     | VDD     | 5V power supply                |

| 7  | NC      | NC      | No Connection                  |

| 8  | NC      | NC      | No Connection                  |

| 9  | VDD     | VDD     | 5V power supply                |

| 10 | NC      | NC      | No Connection                  |

| 11 | ΦROG    | ΦROG    | Readout gate input, active Low |

| 12 | GND     | GND     | Ground                         |

| 13 | NC      | NC      | No Connection                  |

| 14 | NC      | NC      | No Connection                  |

| 15 | VDD     | VDD     | 5V power supply                |

| 16 | GND     | GND     | Ground                         |

| 17 | GND     | GND     | Ground                         |

| 18 | VGG     | NC      | No Connection                  |

| 19 | GND     | GND     | Ground                         |

| 20 | VDD     | VDD     | 5V power supply                |

| 21 | VDD     | VDD     | 5V power supply                |

| 22 | VDD     | VDD     | 5V power supply                |

### **Absolute Maximum Ratings**

The 5 volt supply must not be allowed to exceed 5.5 volts to avoid damage to the device. Operating temperature: -10 to +60°C Storage temperature: -30 to +80°C

### Sample & Hold Mode Selection

The S/H function keeps the readout level constant during each clock period but delays the output by one clock pulse. See timing diagrams.

| Mode | Pin name | Pin number | Note                                           |

|------|----------|------------|------------------------------------------------|

| S/H  | SHSW     | 4          | Sample & hold enable signal, ON: GND, OFF: VDD |

# **Operating Conditions**

# **Recommended Power Supply**

| ltem            | Min | Тур | Max | Unit | Note |

|-----------------|-----|-----|-----|------|------|

| V <sub>DD</sub> | 4.5 | 5.0 | 5.5 | V    |      |

# **Recommended Clock Voltages**

| ltem            | Min                   | Тур             | Max                   | Unit | Note |

|-----------------|-----------------------|-----------------|-----------------------|------|------|

| V <sub>IH</sub> | V <sub>DD</sub> - 0.5 | $V_{\text{DD}}$ | V <sub>DD</sub> + 0.5 | V    |      |

| V <sub>IL</sub> | -0.3                  | 0               | 0.5                   | V    |      |

# **Input Pin Capacitance**

| Item             | Min | Тур | Max | Unit | Note |

|------------------|-----|-----|-----|------|------|

| C <sub>CLK</sub> | -   | 10  | -   | pF   |      |

| C <sub>ROG</sub> | -   | 10  | -   | pF   |      |

# **Electro-Optical Characteristics**

# **Signal Summary**

| ltem                | Min | Тур        | Max | Unit | Note                               |

|---------------------|-----|------------|-----|------|------------------------------------|

| Vsat                | 1.8 | 2.0        | 2.2 | V    | Output saturation level            |

| Vos                 | -   | 2.9        | -   | V    | Output offset level                |

| lvdd*               | -   | 20         | 40  | mA   |                                    |

| Readout Noise       | -   | -          | 500 | uV   |                                    |

| DR                  | -   | 4000       | -   |      | Dynamic range = Vsat/readout noise |

| Output Impedance    | -   | 160        | -   | Ω    |                                    |

| Package Temperature | -   | -10 to +60 | -   | °C   |                                    |

\*operating conditions as specified in the timing diagram

# **Optical summary**

|                            | Symbol | Min | Тур | Max | Unit        | Note                  |

|----------------------------|--------|-----|-----|-----|-------------|-----------------------|

| Sensitivity                | R630   | -   | 420 | -   | V/[uJ/cm^2] | λ = 630nm             |

| Sensitivity nonuniformity  | PRNU   | -   | 10  | -   | %           | 1.0V Output Voltage   |

| Dark voltage nonuniformity | DSNU   | -   | 30  | -   | mV          | 10ms Integration Time |

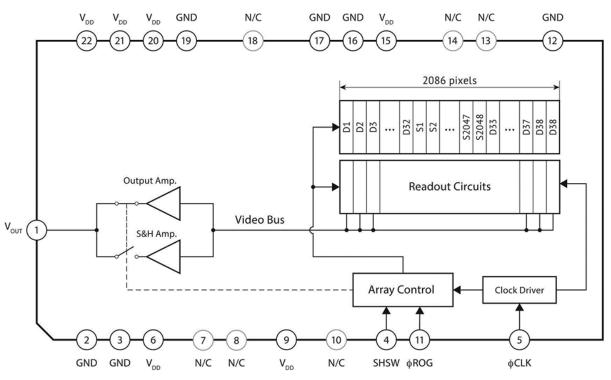

### **ITR-511 Operation**

The ITR-511 consists of a single row of photodiodes connected to two sets of storage and readout registers to permit integration during readout.

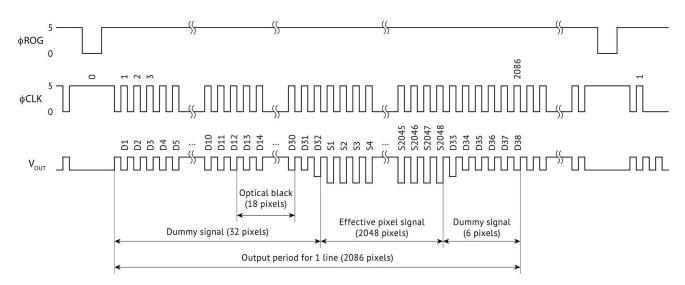

The photodiode row consists of a section of 2048 active photodiodes each  $14 \times 196 \mu m$  in size with 32 dummy photodiodes leading the array and 6 following. 18 optical black pixels (D15 to D32) before and 6 after (D33 to D38) may be used as a dark reference. Systems with wide optical angles at the sensor should avoid using the pixels directly adjacent to the active area for dark reference.

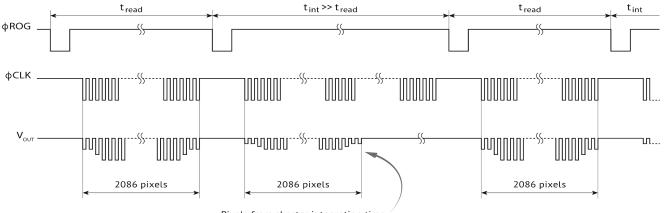

Only two real time signals are required to operate the ITR-511 -  $\phi$ ROG to initiates a readout/integration cycle, and  $\phi$ CLK to read out the pixel data line. A third signal SHSW, allows selection of an internal sample and hold circuit for application circuits which do not provide this function. When the internal S/H is used, the ITR-511 performs a CDS operation on each pixel for noise reduction.

#### **Timing Diagrams**

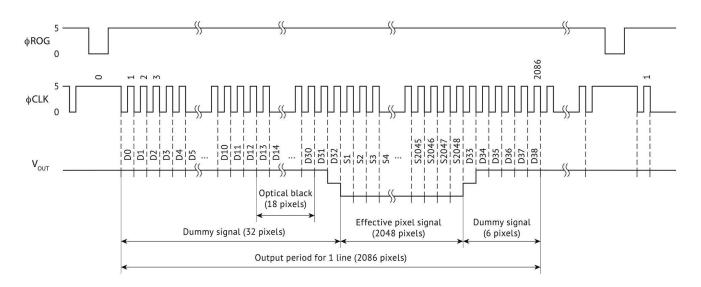

### Overall timing at normal mode

Overall timing at S&H mode

# Clock, ROG and Video Output Timing

### The waveforms and tables are below

| Item                    | Symbol | Min | Тур  | Max | Unit | Note               |

|-------------------------|--------|-----|------|-----|------|--------------------|

| Clock frequency         |        | -   | 2    | 5   | MHz  |                    |

| CLK pulse duty          |        | 40  | 50   | 60  | %    | =100 x t3/(t2+t3)* |

| CLK rise/fall time      | t1     | 0   | 1    | 20  | ns   |                    |

|                         |        |     |      |     |      |                    |

| CLK pulse width         | t2, t3 | 100 | 250  | -   | ns   |                    |

| ROG pulse period        | t7     | 500 | 1000 | -   | ns   |                    |

| ROG, rise & fall        | t8     | 0   | 1    | 20  | ns   |                    |

| CLK - ROG timing        | t9     | 10  | 1000 | -   | ns   |                    |

| CLK - Vout, rise        | t4     | 29  | 37   | 45  | ns   | Delay              |

| CLK - Vout, fall        | t5     | 25  | 33   | 41  | ns   | Delay              |

| CLK - Vout, fall w/ S&H | t6     | 42  | 50   | 58  | ns   | Delay              |

$^{\ast}$  Duty cycles to 75/25 my be tolerated if the clock frequency is 0.5 MHz or below.

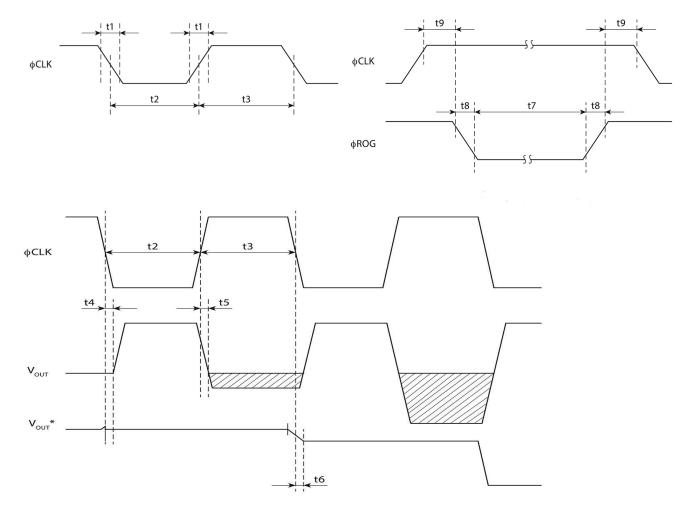

#### Video Output

The output signal from the ITR-511 is a negative-going analog voltage. With no exposure, the output is a stable reset (kTC) level positioned at the output offset voltage, Vos. The reset pulse feedthrough from the ILX-511B is not present in the ITR series devices and the risetimes are facter in the ITR devices. The ITR output is shown with the CCD output shown as a dotted line for reference. Vos may be different in the two devices.

In the ITR-511, the zero signal level after reset may be above the reset level by up to tens of millivolts. The ADC reference should be chosen so that this portion of the signal is not lost.

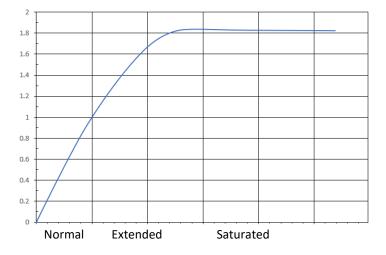

#### Signal vs. Exposure

The ITR-511 is designed to provide a highly linear output over a voltage range similar to that in the ILX-511B. Above that range, the ITR-511B slowly approaches saturation to allow extra dynamic range. In saturation, the ITR-511 does not invert, maintaining a fixed level even with very high levels of overexposure.

In the event that the extra dynamic range is to be used for calculation the user may desire to linearize this section of the curve. This is possible with a single digital table because the shape of the curve is consistent from pixel to pixel and from device to device. However, correction tables must always be based on an accurate and stable zero reference.

#### **Application Circuit**

Operating the ITR-511 requires only providing power and the ROG and CLK signals, taking care to assure the N/C pins are not connected and GND pins are properly grounded. If S&H operation is desired, the SHSW pin is connected to ground. In the S&H mode, the ITR-511 utilizes correlated double sampling (CDS) for noise reduction.

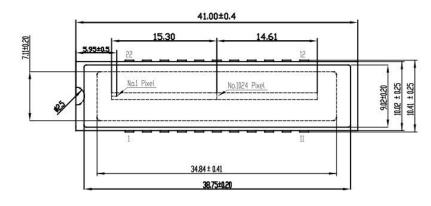

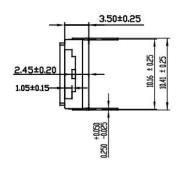

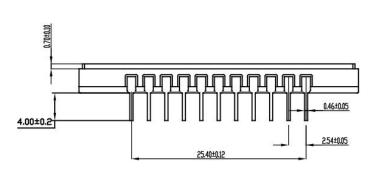

## **Package Outline**

Notes:

- 1 All dimensions are in mm.

- 2 The No. 1 pixel is 5.95±0.05 mm from package end

- 3 The No. 1024 pixel is aligned with the center of the package

- 4 The sensor surfaced is 2.54 $\pm$ 0.4 mm from the package rear

- 5 The index of refraction of the window is 1.5

- 6 The package is black alumina

- 7 The pins are gold-plated iron-nickel alloy 42.

### **Temporary Window Devices**

For applications requiring detection of wavelengths shorter than are passed by the glass window, sensors with removable temporary windows are available. The temporary window may be removed by pulling on the small tab shown in the image below. This should only be done in a static-controlled, dustfree environment to avoid damage to the sensor die. Do not remove the window until processing is ready to start. When the temporary window is removed, the device warranty ends. Care must be taken if a phosphor or fiber optic is to be applied to the die so that the bond wires at the ends of the die are not damaged. Modifications to the sensors should only be undertaken by those with relevant experience.

ITR-511-TW with temporary window in place

ITR-511-TW with temporary window removed

# Significant ITR-511 Variances from the Sony ILX511B

While the ITR-511 will operate properly when inserted in most sockets intended for the Sony ILX-511B, the user should be aware of differences between these devices in configuration and performance. Some are significant, such as the increased sensitivity in the red and near-infrared spectrum of the ITR-511 and the various signal offsets. Others are listed here for completeness in case they require operational changes in certain circuit environments. Changes in optical arrangement should not be necessary.

## **Pixel Height**

The height of the pixel in the ITR-511 is 196 μm, slightly shorter than in the ILX-511B. This is occasioned by a design requirement that the pixel height be an integer multiple of the pixel pitch, which is 14μm.

### Sampling Delay

The nominal delay between the clock transition and stable video output is about 100 ns on the ILX511B while the ITR-511 has a much shorter delay, nominally 37 ns. While the width of the stable part of the video output on the ITR-511 should be sufficient to accommodate this change, some board designs placed the ADC sample position so that the shorter delay causes sampling before the video is stable. In such designs, the sampling position may have to be changed.

# Dark Current

The dark current tin the ITR511 is higher than in the ILX-511B. This may cause uncorrectable offsets or low dynamic range when longer exposures are used. It is recommended that the integration time be kept to no more than 10 msec to avoid potential effects of accumulating dark current.

# **Spectral Response**

The ITR-511 has much higher quantum efficiency in the red and near-infrared regions than the ILX-511B. This may extend the useful detection region of the sensor but it will require calibration of any instrument in which it is used. In applications where the infrared must be blocked, care should be taken to assure that the blocking extends beyond the sensitive band of the ITR-511. The response of the ITR511 is uncharacterized below 380 nm but may extend to the 300 nm window cutoff. Applications involving detection or control in the UV bands will require the user to adequately test the ITR-511 in those bands.

# Alternate Line Offset Voltage

The ITR-511 uses alternating storage registers to permit readout during integration. It is possible that there may be a small (~10 mV) offset between the outputs from these two registers. If the applications software does not use the dark pixel signal to eliminate this offset, it can be bypassed by using data from only every other line.

In the case where the integration time  $t_{int}$  is greater than the read-out time,  $(t_{read})$  the ROG timing can be adjusted such that data from alternate lines is read. In the timing diagram below,  $t_{read}$  is the minimum time required to acquire data for a given line period from 2086 pixels - for example, about 2.1 msec with a 1 MHz clock. Shorter minimum integration times require faster clocking to permit use of this technique.

Pixels from shorter integration time during t<sub>read</sub> can be discarded

#### **Ordering Information**

Orders must be placed with the authorized distributor in the country from which the order is placed. Orders sent to Maxwell-Hiqe headquarters from any area with an authorized distributor will be forwarded to the distributor. Orders sent to Imagica Technologies will be sent to Maxwell-Hiqe and forwarded, if appropriate. Quotations are issued only by the authorized distributor. In some areas, smaller quantities will be sold by authorized dealers. Details can be provided by the distributors in those areas.

| SKU        | Model      | Window       |

|------------|------------|--------------|

| 5560002-01 | ITR-511-SW | Sealed Glass |

| 5560002-02 | ITR-511-TW | Temporary    |

#### **Other Variations**

The ITR-511 can be provided with windows made of other materials or with anti-reflective or other coatings. Contact Maxwell-Hige for details

#### Packaging and Marking

Generally, devices are shipped in antistatic tubes marked with the SKU, Model and quantity. Individual devices may be lasermarked with revision, date and lot codes on the bottom surface. Small quantities packed in antistatic boxes or other suitable containers may be supplied in some areas.

#### Handling and Storage

The ITR-511 is a CMOS integrated circuit. While it is provided with some protection from static during handling, normal precautions should be taken including grounding of surfaces and operators and avoidance of any static discharge near the device. Devices should be stored in antistatic tubes or boxes in areas where the temperature will not exceed the absolute maximums. Glass windows should be protected from abrasion and devices with temporary windows removed should be protected from unnecessary contact with the sensor die surface. Devices with the temporary windows removed have no protection from static. During soldering, the package temperature should not exceed the stated absolute maximum. These devices are not hermetically sealed.

#### **Restrictions On Use**

IMAGICA SEMICONDUCTOR DEVICES ARE NOT DESIGNED OR AUTHORIZED FOR USE IN: (A) SAFETY CRITICAL APPLICATIONS SUCH AS LIFE SUPPORTING APPLICATIONS THAT INCORPORATE, ACTIVE IMPLANTED DEVICES OR SYSTEMS WITH PRODUCT FUNCTIONAL SAFETY REQUIREMENTS; (B) AERONAUTIC APPLICATIONS; (C) AUTOMOTIVE APPLICATIONS OR ENVIRON-MENTS; (D) AEROSPACE APPLICATIONS OR (E) ENVIRONMENTS. WHERE IMAGICA SEMICONDUCTOR DEVICES ARE NOT DE-SIGNED FOR SUCH USE. YOU SHALL USE THE IMAGICA SEMICONDUCTOR DEVICE AT YOUR SOLE RISK, EVEN IF IMAGICA HAS BEEN INFORMED IN WRITING OF SUCH USAGE, UNLESS AN IMAGICA SEMICONDUCTOR DEVICE IS EXPRESSLY DESIGNATED BY IMAGICA AS BEING INTENDED FOR "AUTOMOTIVE, AUTOMOTIVE SAFETY OR MEDICAL" INDUSTRY DOMAINS ACCORDING TO IMAGICA SEMICONDUCTOR DEVICE DESIGN SPECIFICATIONS.

Imagica Technology, Inc., reserves the right to change products or information without notice. This document does not guarantee supply of any product described herein. This document does not convey any license for design, manufacture or use.

Trademarks are property of their respective owners.

Manufactured by: Imagica Technology, Inc. Vancouver, BC, Canada www.imagica.technology Distributed Globally by: Maxwell-Hiqe Corporation Tucson, AZ, USA www.maxwell-hiqe.com Local Sales by: